Second Level Address Translation

Second Level Address Translation (SLAT), auch als Nested Paging bezeichnet, ist eine hardwareunterstützte Virtualisierungstechnologie, die eine effizientere Umsetzung von Shadow Page Tables[1] im Vergleich zu einer softwarebasierten Virtualisierungslösung erlaubt.AMD implementierte SLAT zuerst durch eine von AMD als Rapid Virtualization Indexing (RVI) bezeichnete Technologie und unterstützt diese seit der Einführung der dritten Opteron-Prozessorgeneration (Codename Barcelona) 2007 in ihren Prozessoren.[2]Mit der Nehalem-Prozessorfamilie führte Intel 2008 eine Implementierung von SLAT ein, die von Intel selbst als Extended Page Tables (EPT) bezeichnet wird.[3][4][5]Sie wird in bestimmten Prozessoren der Core-i7-, Core-i5- und Core-i3-Klasse unterstützt.

Überblick

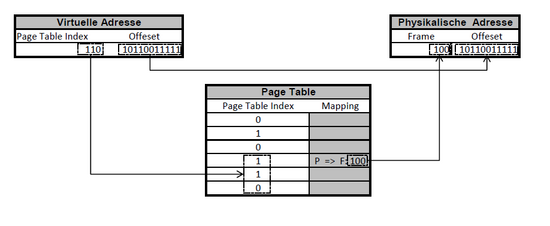

Moderne Prozessoren unterscheiden bezüglich Speicherverwaltung die Konzepte des physischen und des virtuellen Speichers. Anwendungsprozesse greifen ausschließlich auf den virtuellen Speicher zu. Diese Zugriffe werden vom Prozessor bzw. der Memory Management Unit (MMU) als Komponente des Prozessors vom virtuellen in den physischen Adressraum umgesetzt. Die Zuordnung wird vom Prozessor in sogenannten Page Tables oder Translation Lookaside Buffers (TLB) gespeichert. Der Begriff „virtueller Speicher“ hat nichts mit dem Speicher virtueller Maschinen zu tun, sondern ist ein Konzept, das unabhängig von der Virtualisierung bereits in modernen x86-Prozessoren eingesetzt wird und von allen modernen Betriebssystemen genutzt wird.

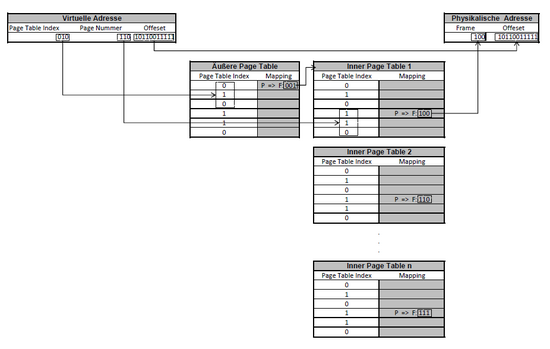

Da solche Page Tables aufgrund der großen Speicher moderner Systeme sehr groß werden können, wurde das Konzept zu einem mehrstufigen Page Table Lookup ausgebaut, bei dem mehrere Stufen von Page Tables zum Einsatz kommen. Damit können nicht benötigte Page Tables leichter in externen Speicher ausgelagert werden und generell lässt sich leichter mit großen Adressräumen umgehen.

Kommen nun zu diesem Konzept noch der Hypervisor und mehrere virtuelle Maschinen hinzu, wird eine weitere Adressumsetzung benötigt. Diese weitere Adressumsetzung erfolgt zwischen den Speicheraufrufen der Virtuellen Maschine und den dem Hypervisor zugeordneten Speicherbereichen. Ist keine Hardwareunterstützung dafür vorhanden, muss der Hypervisor diese Umsetzung erledigen, um den Speicher dann über die MMU und den oben genannten mehrstufigen Mechanismus anzusprechen. Diese doppelte Umsetzung führte zu erheblichen Performanceverlusten beim Betrieb von virtuellen Maschinen im Vergleich zum Betrieb direkt auf der Hardware.

Die Prozessorhersteller erkannten dieses Performancepotential und erweiterten den ohnehin schon mehrstufigen Page-Table-Mappingprozess um weitere Stufen, die das Mapping für die Virtualisierung erledigen. Diese Technologie wird aufgrund der weiteren Stufen des Mappings für die Virtualisierung "Second Level Address Translation" (kurz SLAT) genannt. Im Vergleich zur softwarebasierten Lösung, wie oben beschrieben, erhoffte man sich dadurch erhebliche Performancezugewinne für die Virtualisierung.

Wenn SLAT und mehrstufiges Page Table Mapping gemeinsam verwendet werden, verdoppelt sich die Zahl der zu durchlaufenden Mappingstufen bei gleicher Adressgröße der physischen Gastadresse und der virtuellen Gastadresse und gleicher Größe der Page Tables. Diese Tatsache macht Caching-Mechanismen für die Zwischenlevels von Host- und Gast-Page-Tables sehr wichtig, da nicht immer alle Tabellen im Speicher gehalten werden können und durch geschicktes Caching die Zugriffszeiten trotzdem gering gehalten werden können. Es ist deswegen auch sinnvoll, große Page-Table-Größen für die Host Page Tables zu wählen, um die Zahl der notwendige Page-Table-Levels zu verringern.

Implementierungen

Extended Page Tables

Extended Page Tables (EPT) ist eine x86-Virtualisierungstechnologie der zweiten Generation für die Memory Management Unit (MMU). Sie wird unter anderem in bestimmten Prozessoren der Core-i7-, Core-i5- und Core-i3-Klasse unterstützt.[6]

Mit der Westmere-Reihe von Prozessoren ergänzte Intel ein Feature, welches es erlaubt, logische Prozessoren direkt im "Real Mode" zu starten. Das Feature wird von Intel "Unrestricted Guest" genannt und setzt das EPT-Feature voraus.[7][8]Laut einem VMWare-Aufsatz heißt es: "EPT provides performance gains of up to 48 % for MMU-intensive benchmarks and up to 600 % for MMU-intensive microbenchmarks", d. h., es können durch EPT laut VMWare Performancesteigerungen zwischen 48 % und 600 % erzielt werden, obwohl diese Messungen sehr stark davon abhängen, welche Anwendungsfälle den Tests zugrunde lagen. VMWare fand hierzu heraus, dass Virtualisierung unter Verwendung von EPT in bestimmten Grenzfällen sogar langsamer sein kann, als unter Verwendung einer softwarebasierten Methode des Hypervisors.[9]

Rapid Virtualization Indexing

AMD-Opteron-CPUs ab der 0x10 Barcelona Line, Phenom-II-CPUs und nachfolgende Prozessorgenerationen unterstützen eine fortgeschrittene Virtualisierungstechnologie, die von AMD "Rapid Virtualization Indexing" genannt wird (während der Entwicklung wurde sie als "Nested Page Tables" bezeichnet) und die SLAT implementiert.[10][11]

In einem VMware-Forschungsaufsatz wurde dargestellt, das RVI bis zu 42 % Performance-Gewinn verglichen mit der softwarebasierten Implementierung erreichen kann.[12] Tests, die durch Red Hat durchgeführt wurden, zeigten eine Verdoppelung der Performance für OLTP-Benchmark-Tests.[13]

Support durch Hypervisoren

Die folgenden Hypervisoren unterstützen SLAT:

- Hyper-V für Windows Server 2008 R2, Windows 8 und spätere Versionen.[14] Windows 8 Hyper-V setzt SLAT bzw. EPT voraus.[15][16]

- KVM 2.6.26 und spätere Versionen[17][18]

- VirtualBox 2.0.0 und spätere Versionen[19]

- VMware ESX/ESXi 3.5 und spätere Versionen[12]

- Xen 3.2.0 und spätere Versionen[20]

- bhyve unterstützt und benötigt EPT[21]

Es sollte beachtet werden, dass einige Hypervisoren zwingend EPT- oder RVI-unterstützende Prozessoren benötigen, da sie selbst kein softwarebasiertes Page Table Mapping mehr unterstützen. Die Liste ist diesbezüglich nicht auf dem letzten Stand.

Siehe auch

Weblinks

- Patent US7428626B2: Method and system for a second level address translation in a virtual machine environment. Angemeldet am 8. März 2005, veröffentlicht am 23. September 2008, Anmelder: Microsoft Corporation, Erfinder: Rene Antonio Vega.

- Second Level Address Translation Benefits in Hyper-V R2

- Virtualization in Linux KVM + QEMU (PDF)